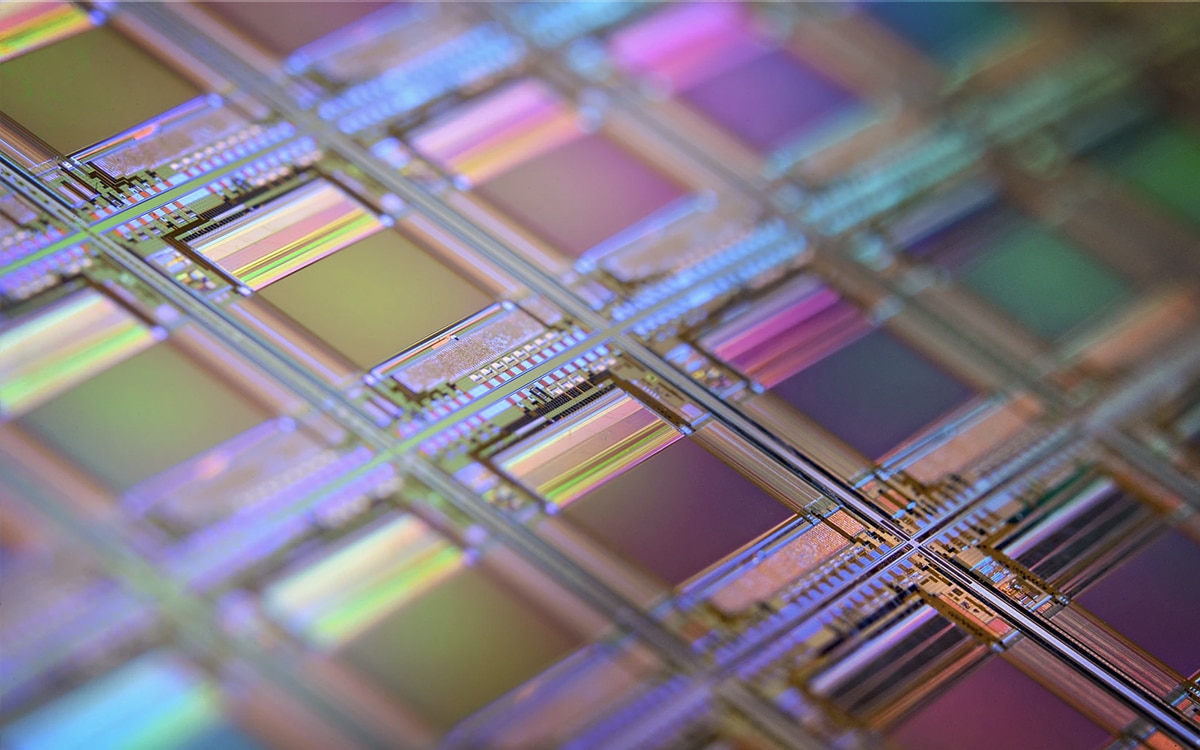

iPhone, Android : TSMC et Samsung travaillent déjà sur des puces en 2 nm plus autonomes et puissantes

TSMC et Samsung les deux plus gros fondeurs de la planète travaillent déjà sur les prochaines générations de puces des iPhone et smartphones Android. Avec le passage au 3 nm et in fine au 2 nm. De quoi réduire encore significativement la consommation énergétique du composant tout en le rendant encore plus puissant.

Pour la première fois le grand public peut acheter des iPhone 12 dotés d'une puce gravée en 5 nm. La finesse de gravure est primordiale dans l'industrie mobile, car elle permet de mettre nettement plus de transistors dans un espace réduit tout en réduisant significativement la consommation énergétique. Or, Apple comme de nombreuses marques ne dispose pas de sa propre fonderie.

Et fait donc appel aux leaders du secteur, notamment TSMC depuis maintenant pas mal de générations. La nouvelle puce A14 Bionic embarque ainsi 11,8 milliards de transistors contre les 8,5 milliards de la puce A13 Bionic des iPhone 11. Bien sûr on pourra objecter que Apple n'est pas seul sur le 5 nm : Huawei vient de dévoiler ses nouveaux Mate 40 et Mate 40 Pro, avec une nouvelle puce Kirin 9000 elle aussi gravée en 5 nm et qui dispose d'encore plus de transistors. Mais dans le cas de Huawei, la situation est compliquée par les sanctions américaines.

Seuls une poignée de fondeurs ont accès aux équipements indispensables pour graver des puces en 5 nm et au-delà

TSMC et les fondeurs concurrents ne peuvent en effet plus fournir le constructeur en composants depuis que de nouvelles sanctions américaines sont entrées en vigueur. Ces sanctions interdisent aux firmes qui utilisent des propriétés intellectuelles américaines de fournir Huawei en composants sans obtenir l'accord préalable du Département du Commerce. Autorisation que n'a pas obtenue TSMC pour Huawei. En conséquence, sur les 15 millions de puces Kirin 9000 commandées par le constructeur chinois, seules 8 millions ont effectivement pu être livrées.

Ce qui devrait très fortement limiter les ventes de Huawei à court et moyen terme. D'autant plus que Huawei n'avait pas l'intention d'utiliser le Kirin 9000 uniquement sur les Mate 40 – mais aussi dans ses solutions de réseau 5G et son smartphone pliable Mate X2. Seuls un autre acteur est ainsi censé rejoindre le club du 5 nm dès l'année prochaine : Samsung avec sa prochaine puce Exynos et le Snapdragon 875 qu'il devrait graver pour Qualcomm. Or, Samsung et TSMC travaillent déjà avec l'équipementier néerlandais ASML sur la gravure en 3 nm et 2 nm.

L'occasion de se plonger dans l'augmentation des finesses de gravure, ainsi que dans le rôle central d'équipementiers comme ASML pour délivrer des puces toujours plus performantes. Au passage, Huawei cherche depuis le début de la guerre commerciale, des alternatives pour éviter de voir son approvisionnement en puces performantes disparaître. La Chine dispose bien d'un fondeur national, SMIC, mais ses procédés de gravure restent encore en retrait de la concurrence (14 nm et bientôt du 7 nm).

Les innovations se multiplient à mesure que l'on atteint des limites fondamentales

Ce qui est le cas justement parce que des équipementiers comme ASML n'ont plus le droit de fournir ces acteurs en machines dernier-cri. Plus la finesse de gravure réduit, plus on repousse les limites de ce qu'il est techniquement possible de faire, d'autant que des effets étranges apparaissent. Il faut ainsi adopter des astuces toujours plus sophistiquées pour garder une précision constante de gravure, et éviter les effets de fuites de courant, ou de perturbations qui prennent le dessus passé un certain seuil. Pour le 5 nm, il a ainsi fallu développer un procédé de lithographie UV Extrême (EUV).

Comprenez que les différentes couches sont gravées sur les wafers de silicium avec des longueurs d'onde particulièrement courtes. Le design des portes des transistors est lui aussi adapté pour éviter les effets quantiques qui prennent le dessus à cette échelle (on parle d'éléments qui ne font que quelques atomes de large). Or, pour délivrer des gains de performances toujours plus importants, TSMC, ASML et d'autres fondeurs comme Samsung s'intéressent aussi à l'augmentation du nombre de couches de composants sur chaque die.

Ces couches permettent à la fois de créer des composants plus complexes – ce qui est indispensable à ces échelles. Tout en complexifiant le design de la puce. Ainsi pour l'heure, TSMC utilise actuellement un procédé 5 nm qui permet de graver jusqu'à 14 couches sur le même composant. Le passage au 3 nm devrait délivrer à lui seul une puissance en hausse de 15 % et une consommation énergétique réduite de 30 % à un niveau de complexité et nombre de transistors égal.

Mais il est sans doute possible de faire encore mieux : ASML développe une technologie qui permettra de graver jusqu'à 20 couches sur le même die en 3 nm. Un progrès qui devrait bénéficier aussi bien aux SoC pour smartphones qu'aux puces mémoire DRAM. Avec le 3 nm, TSMC optera pour un design de transistors dit FinFET : il s'agit en fait de transitors dotés de deux portes. Le nom FinFET vient de la forme de certaines régions du composants qui forme des sortes de lamelles sur la surface du die. Cela permet d'augmenter la fréquence, tout en augmentant la densité des composants.

Pour le passage au 2 nm TSMC va encore changer le design des transistors pour passer à la technologie GAAFET (Gate All Around) développée par Samsung en parallèle de la technologie MBCFET pour aller au-delà de 3 nm. On devrait ainsi voir des innovations passionnantes au cours des prochaines années, à mesure que l'on se rapproche des limites fondamentales de la gravure sur silicium. En attendant peut-être de trouver des alternatives.

Source : PhoneArena